Masendav august.

Sugulastel ja kodus lendas kokku 3 toiteplokki ja üks kõvaketas. Muidugi tassiti kõik mulle näha ja süüdi tunda, sest kes siis veel arvutite eest vastutab :-)

Kõik masinad olid IT Kolledži vanad HP-d (d530S ja D5S SFF). DS5-ga jamama ei hakanudki, liiga vana ja selle toiteploki skemaatiline lahendus on remondiks tülikam ja kui aus olla, siis kunagi varem proovisin juba üht parandada, mis lõppes mitmesaja krooni ulatuses uute komponentide tapmisega.

Üsna pea sai selgeks, et probleem on üle maailma tuntud, d530S ja teiste HP arvutite toiteplokkide probleemiks on komponentide fikseerimiseks kinnitatud liim, mis vanandes ja kuumuse mõjul teiseneb pisut elektrit juhtivaks. Natuke augustiniiskust juurde ja ühel ilusal hetkel ületatakse võrgupinge nivool töötavate komponentide taluvuspiir ning edasine on nagu laviin, selle käigus kõrbeb ligi 10 komponenti. Kõige naljakam, et sulavkaitse toetab kogu seda hävingut kuni täieliku finaalini, astudes tulest ja suitsust välja nagu tõeline terminaator ilma ühegi kriimuta.

OK, maailmakogemus ja juhised on siin: http://webdevsys.com/d530psuRepairNotes.htm

Peaaegu kõik komponendid on Oomipoest saadavad. P-N-P transistorid said isegi kaks korda ägedamad kui originaalid (tegijaks osutus ZTX751). Siiski, kõrbenud väljaviiguga 250pF 1kV kondensaatori asenduse leidsin ainult Tevalo/Elfaelektroonia valikust.

Toiteplokid on päris komplitseeritud disainiga, põhiplaadil on veel kaks tütarkaarti, millest üks on autonoomne 5V käivituspinge muundi. Ühel toiteplokil (olgu see A) kõrbes ainult põhiplaadi võrgupinge osa, aga kannatada said ka voolurajad. Teisel (olgu see B) põles maha ka 5V tütarplaat. Aga B põhiplaat nägi parem välja.

Seepärast saigi alustatud B-st, võttes A-st korras tütarplaadi.

Paraku ei võtnud B pärast kõikide põlenud ja sulanud komponentide väljavahetamist täit vedu. Tütarplaat toimis, aga sisselülitamisel käis plokist läbi ainult üks impulss, ventilaator nõksatas, aga ilmselt oli miskit tagasisideahelates ikka sassis.

Aga A-ga tuli õnneks bingo, kõrbenud emaplaati kannatas puhastada ja radasid jätkata, epoksiidliimiga tugevdasin komponentide püsivust kõrbenud läbiviikudes. Tütarplaat oli ju A-l niigi korras.

Muidugi ei tasu aeg ja vaev end ära. Diagnostikaks on vaja normaalset multimeetrit, komponente tuleb kataloogidest otsida ja neil poes järel käia (kui täpne olla, siis Fairchild FQA9N90C MOSFET transistorid tellisin eBayst. Tulid Hong Kongist nädalaga kohale, 10$ väärtusega ümbrik tolli ei huvitanud).Tahmanud ja kõrbenud kõrgpinge osa remont nõuab mitmeid tunde aega ja kõrgendatud tähelepanu.

Aga reinkarnatsiooni moment on imeline :-)

PS. Lisan mõnede läbipõlenud komponentide nominaalid, mida veebijuhendis ei leidunud: C10 - 250pF 1kV; R12 - 1 oom 1W, R18 - 6,8 oomi.

PS. Hiljem (16. septembril) sain käima ka põhiplaadi B. Selgus, et tagasisideahela optron võib olla ka teistmoodi läbi põlenud kui ainult lühisega. Kokkuotsitud kuuest plokist on nüüdseks reinkarnatsiooni läbinud 4. Ühel on läbi tütarplaadi trafo mähis (katkestuses), sellist elementi Oomipoe ja Elfaelektroonika kataloogides ei leidu.Aga viienda reinkarnatsioon on veel võimalik. :-)

SUMMARY

Kokku sai 7-st plokist korda kuus, remontimata jäi ainult üks juba nimetatud põlenud mähisega trafo pärast, mille tarneks lihtsat viisi Googlest ei paistnud. Aga kolmel kõige kauem allumatust näidanud plokil oli viga tütarplaadi sekundaarahelates, lühistunud oli ilmselt ülepinge kaitse funktsiooni täitnud 6V zener diood D61.

Friday, September 3, 2010

Thursday, April 29, 2010

Spartan3 ja PicoBlaze programmimälu värskendamine üle JTAG liidese

Kogu vajatav atribuutika selleks on kaasas PicoBlaze protsessori assembleri KCPSM3 failidega XILINX PicoBlaze lehelt.

Tähelepanu tuleb pöörata lühijuhendile JTAG_loader_quick_guide.pdf, mis annab üsna ammendava ja pildirohke seletuse.

Kui see protseduur on korra juba läbi tehtud, siis järgmistel PicoBlaze koodi uuenduste kordadel piisab lahtihoitud käsu- ja IMPACT akendes väheste korralduste kordamisest, see läheb tõesti nobedalt.

Tähelepanu tuleb pöörata lühijuhendile JTAG_loader_quick_guide.pdf, mis annab üsna ammendava ja pildirohke seletuse.

- Asendada mälu alusfailid ROM_form.vhd ja ROM_form.v, mis vaikimisi on koopiad failidest Normal_ROM_form.vhd ja Normal_ROM_form.v.

Kopeeri nende asemele failid JTAG_Loader_ROM_form.vhd ja JTAG_Loader_ROM_form.v. - Põhimoodulis, mis paigaldab KCPSM3 ja selle nüüdseks kahepordilise programmimälu, tuleb tagada JTAG-laaditava ROM-mooduli poolt genereeritava RESET-signaali jõudmine protsessorisse. Kui on soov protsessori RESET-i sõltumatult väljastpoolt juhtida, siis tuleb lihtsalt vastavad signaalid liita, nt.:

reset <= CLEAR or proc_reset; -- siin CLEAR on minu kasutatud välise RESET-signaali nimi - See pole veel kõik - tõenäoliselt tabab teid sünteesil teade, et prog_rom.vhdl failis on puudu komponent BSCAN_VIRTEX2. Tõepoolest, sellist pole Xilinx Unisim teegis olemaski, küll on seal aga BSCAN_SPARTAN3 - ja mis võiks olla parem! S.t. prog_rom.vhdl failis tuleb teha vastav asendus, ju on universaalsena mõeldud KCPSM3 paketis vaiikimisi üht teist Xilinx kiibisarja silmas peetud.

Veelgi enam - kuna prog_rom.vhdl fail on genereeritud ROM_form.vhd aluspõhjast, siis tuleb see asi korda ajada hoopis aluspõhjas ROM_form.vhd, et uuel programmi kompileerimisel sama tüli ei tekiks! - Kompileerida ja laadida Spartan3 arendusplaadile mistahes kanali/rakenduse kaudu.

- Programm kompileeritakse nagu tavaliselt, kuid sorry, sobib ainult KCPSM3 kompilaator, mitte pBlazIDE. Viimane ei genereeri väljundiks vajalikku .hex formaadis failil.

- Järgneb rida hex faili teisendusi, milleks on KCPSM failide hulgas olemas sobiv käsufail jtag_loader.bat, mis esmalt kontrollib vastava Boundary_scan konfiguratsioonifaili (hex2svf.cnf) olemasolu töökaustas ja puudumisel loob selle dialoogis kasutajaga. Sisendiks tuleb anda Xilinx kiibi tüüp (Spartan3 on 4) ja kirjeldada ahelat, s.t. Spartan3-le eelnevaid ja järgnevaid kiipe ahelas. No Nexys2 arendusplaadil on üks järgnev mäluelement xcf04s, mille kood dialoogis on 8, tavaahel on näha joonisel:

- Pärast teisendusi laadib jtag_loader.bat plokk-ROM-i sisu (.xsvf faili) ka paralleelpordis oleva JTAG liidese kaudu Xilinx kiipi.

USB-liidese kaudu laadimiseks on lihtsaim kasutada Xilinx IMPACT rakendust (alternatiiviks oleks modifitseeritud .bat faili, mis sama IMPACT-i käsurežiimis rakendab). IMPACT graafilises režiimis kasutamiseks tuleb kustutada jtag_loader.bat-failis viimane käsk playxsvf %1.xsvf.

IMPACT käivitatakse puhta tööväljaga. Kui eelenvast tööst on Boundary-scan ahel tööväljal, siis tuleb see kustutada (klikkides hiire vasaku klahviga elementidel ja ükshaaval kustutades Del-klahviga).

Seejärel tühjal tööväljal parem hiire klikk ja valida hüpikmenüüst Add Xilinx Device.

Valida töökaustast vastav .xsvf fail (minul prog_rom.xsvf), mille järele ilmub tööväljale ahel XSVF elemendiga.

Valida element parema hiire klahviga ja hüpikmenüüst valida Execute XSVF/SVF.

Prototüüpplaadil võib olla jälgitav (kui programm jooksis ja midagi dünaamiliselt esitas) programmi seiskumine ja toimub PicoBlaze lähestamine. Voila!

Kui see protseduur on korra juba läbi tehtud, siis järgmistel PicoBlaze koodi uuenduste kordadel piisab lahtihoitud käsu- ja IMPACT akendes väheste korralduste kordamisest, see läheb tõesti nobedalt.

Sunday, April 4, 2010

DMX 4-kanaliline kontroller PAR56-le

Riist- või tarkvara disaini näidisprojekt

Antud artiklis on juttu nö elektroonika hobiprojektist, mis siiski sai autorilt enam tähelepanu, kuna lahendust sai otsitud nii riist- kui tarkvaralisena, seda küll ilma koosdisaini metoodikat kasutamata. Sellest siis ka nihe pealkirjas – mitte riist- ja tarkvara koosdisain vaid riist- või tarkvara disain. Tulemus võib siiski väärida järeletegemist kuna valminud kontroller on küllalt universaalne seade.

Projekti algatas lihtne juhtum – tekkis vajadus lisada 3-värvilisele LED-prožektorile PAR56, mis on küll varustatud sisemise kontrolleriga ja mõningate DIP-lülitilt valitavate valmis värvusskeemide ning värvivahetusprogrammidega, täielikku häälestusulatust lubav lihtne juhtseade. Valgustusseadmete juhtimiseks on olemas ka valmispulte, kuid need olid ühe pro˛ektori kodukasutaja jaoks „liiga head“.

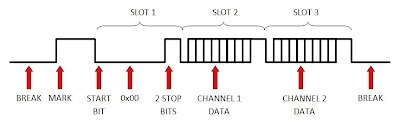

Nagu lähemal uurimisel selgus, on DMX (täpsemini DMX512 [1]) füüsikalisel tasandil sama, mis RS485 [2], s.t. diferentssignaali kasutav jadakoodi andmevahetusstandard. DMX protokoll on lihtne, lausa robustne – kõige lihtsamal juhul ühesuunaline andmepakett, milles iga bait tähendab infot ühe DMX kanali kohta. Konkreetne DMX-seade võib kasutada oma funktsioonide juhtimiseks mingit kanalite vahemikku paketist. Ühte paketti mahub kuni 512 kanalit, selle ulatuse ärakasutamine sõltub juba otstarbest, pakett võib olla palju lühem, olles määratud vajatavate kanalite arvuga. Pakettide vahel on paus (BREAK) loogilisel nivool „0“. Iga pakett algab minimaalselt 12µs märgisega MARK (nivool „1“), millele järgneb startkood (DMX seadmetel on üldjuhul koodiks 0x00) ja seejärel juba kanalid alates number 1-st. Jadakood saadetakse välja andmesõnadena (slot) kujul – startbitt (loogiline „0“), 8 andmebitti alates nooremast ja kaks stoppbitti (loogiline „1“). DMX standard defineerib veel pakettide vahelise pausi minimaalse kestvuse (92 µs ) ja ülekandekiiruse, milleks on üsna aukartustäratav 250kboodi – ühe bit kohta 4 µs aega. Maksimaalse paketipikkuse ja minimaalse pausi korral jõutakse sekundis saata 44 paketti, samas kui seadmed peaksid säilitama tööre˛iimi ka siis kui tuleb ainult üks pakett sekundis. Eri kanalid võivad olla mõeldud eri seadmetele kõik ühe ja sama RS485 signaaliahela (daicy-chain topoloogia) küljes. Iga seade loeb ühisest paketist välja just temale seatud kanalite andmed.

PAR56 prožektor on häälestatud reageerima paketi nelja esimese kanali andmetele, mis on siis vastavalt:

1. Punased LED-d (koodid 0-255),

2. Rohelised LED-d (koodid 0-255)

3. Sinised LED-d (koodid 0-255)

4. Heledus (koodid 0-189), vilkumine (koodid 190-250) ja mittedefineeritud (koodid 251-255).

Niisiis, lähtudes otse standardist, tuleks saata sagedusel 250kHz vähemalt kord sekundis välja 58-bitiline pakett-vektor. Juhul kui PAR56 kõigi kanalite väärtuseks on 127, oleks pakett järgmine (algus paremal):

"1101111111011011111110110111111101101111111011000000000111" ====>

Kolm „111“ alguses annavad täpselt vajaliku 12µs MARK-sündmuse.

Kui nüüd juhtseadme projekteerimiseks läheb, siis selgub, et kõige lihtsama mikrokontrolleriga seda ära ei teegi, hädavajalik on riistvaralise jadaside mooduli olemasolu (UART). Ilma selleta oleks paketi saatmine protsessorile üle jõu käiv - tavaline mikrokontrolleri töökiirus on suurusjärgus 1 µs käsutsükli kohta, mille korral jõuaks protsessor teha ühe biti väljasaatmise jooksul vaid 4 käsku – sellest ei piisa, et andmeid ette valmistada. UART moodul võtaks bitthaaval andmesõna formeerimise vaeva enda peale ja baithaaval andmeid ette sööta jõuab siis ka palju aeglasem protsessor (baidi saateaeg koos START ja kahe STOP-bitiga on 11 x 4 = 44 µs). Signaali pausiaeg on DMX korral piisavalt pikaks venitatav (kuni 1 sekund), et selle jooksul mistahes protsessor mistahes kasutajaliidese töötlemisega toime tulla.

Kuidas oleks aga riistvaraline lahend väliprogrammeeritaval kiibil? Tegelikult väga elementaarne – riistvaras võib kuitahes pikki bitivektoreid moodustada, vajalikud andmebaidid tuleb vaid vektorisse õigesse positsiooni omistada ja 250kHz taktiga väljundisse suunata. Kasutajaliidest võib riistvara töödelda paralleelselt jadakoodi väljastamisega, selleks jätkub ressursse ka kõige tagasihoidlikumas FPGA-kiibis.

TxDI <= dmxvector(0); -- vektori kõige parempoolne bitt väljundisse DMX-signaaliks

Tervikkirjeldusse kuulub veel komponent, mis tagab signaalide dmxred,dmxgreen, dmxblue ja dmxch4 juhtimise kasutaja poolt. Võib öelda, et kood töötas esimesest katsest, lubades pro˛ektorit vabalt juhtida ning katsetamise käigus proovida läbi erinevaid kasutajaliideseid.

Eksperiment: Tarkvaraline lahendus

Tarkvara kandjaks protsessor Microchip PIC16F88, arendustarkvaraks Microchip IDE (vabavara) ja CCS C-kompilaator PCM (kommertsprodukt [4]).

Mikrokontroller PIC16F88 on lihtne 8-bitilise arhitektuuriga 18-väljaviiguline protsessor, mis on paljude lisade hulgas varustatud asünkroonse jadaliidesega (USART). Dokumentatsiooni järgi suudab USART protsessor 4MHz sisemise takti korral genereerida vabalt 250kboodist jadasignaali.

Koodi kirjutamisel tuli tõdeda mitmeid üllatusi, mis nõudsid paljusid katseid enne kui tulemus PAR56 pro˛ektorit allutama hakkas:

1. Selgus, et PIC16F88 PortA on vaikimisi analoogsisenditena häälestatud, s.t. digitaalsisenditena kasutamiseks tuli analoogmoodul välja lülitada. Muidugi oli see ka dokumentatsioonis kirjas.

2. PIC16F88 USART ei ole otseselt häälestatav kahe stop-bitiga jadaprotokollile. Siiski, kuna andmeüksuse suurus võib olla ka 9 bitti, siis oli võimalik sättida 9-s bitt täitma esimese stopp-biti rolli (konstantselt „1“). Seda tuli siis teha väljaspool CCS PCM kompilaatori standardfunktsioone (assembleris).

3. PIC16F88 USART ei toetanud otseselt DMX protokolli. Tõsi küll, USART oskab genereerida väidetavalt RS485-toetuseks mõeldud ENABLE-signaali, mis on aktiivne andmesõna saatmise ajal, kuid ei oleks taganud vajalikku MARK signaali kestvust ja pealegi muutub ENABLE korraks passiivseks ka andmesõnade vahel, mis rikuks DMX-paketi kuju.

4. USART väljund jääb andmesõnade saatmise vaheajal kõrgeks „1“ . Kuna DMX protokoll nõuab BREAK tingimuse moodustamist, mille ajal signaal on „0“, siis lõppkokkuvõttes tuli BREAK ja MARK tingimused samuti genereerida väljaspool kompilaatori standardfunktsioone.

Nimetatud erisused tegid iseenesest triviaalse ülesande lahendamise ajakulukas ja väljundsignaali tegeliku kuju tuvastamiseks ja häälestamiseks tuli kasutada digitaalostsillograafi.

Lõppjäreldused

Riistvara (Nexys 2 ja Xilinx FPGA)

Tuleb tunnistada, et mõlematel variantidel on plusse ja miinuseid. Kiireks prototüüpimiseks on riistvaraline lahendus FPGA-l vägagi sobiv ja eriti ladusalt läheb standardikohase protokolli genereerimine. Samas iga arendusplaadi väline lisafunktsionaalsus nõuab väliste riistvaraliste moodulite lisamist (näiteks mikrokontrolleris on mugav sisemine EEPROM, mida võib kasutada oleku säilitamiseks seadme väljalülitatud olekus; Nexys 2 arendusplaadil tulnuks sellise funktsionaalsuse saamiseks lisada mälukaardi moodul).

Tarkvaraline lahendus sobib lõppteostuseks paremini, kuid nõuab protsessori ning kompilaatori dokumentatsiooni põhjalikku uurimist, et kõigi võimaluste ja tõkete rägastikus leida sobiv tee protokolli ja muu funktsionaalsuse teostuseks.

Lõpptulemus, nelja kanaliga ja nelja mäluga DMX kontroller koos PAR56 prožektoriga on näha järgmisel fotol:

Seadme kasutajaliidesel on neli nuppu värvide valikuks (ühtlasi ka mälupesade valikuks), nupud valitud värvi väärtuse kerimiseks ning värvuskombinatsiooni salvestus- ja taasesitusnupud.

Projektifailid on veebis [5]: PIC16F88-ga DMX-kontrolleri skeem ja trükkplaat CadSoft Eagle failidena, kontrolleri tarkvara CCS PSM C-ning kompileeritud HEX-koodis ning Nexys 2 arendusplaadile mõeldud kontrolleri tipptaseme komponendi kirjeldus VHDL keeles.

Viiteid

1. DMX512, http://en.wikipedia.org/wiki/DMX512

2. Jan Axelson, Designing RS-485 Circuits, http://lms.uni-mb.si/~meolic/students/mpk/designingRS485.pdf

3. Nexys 2 FPGA board, http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,400,789&Prod=NEXYS2

4. CCS Compilers, http://www.ccsinfo.com/content.php?page=compilers

5. Kontrolleri projektifailid (tarkvara uusim versioon dets. 2011!!!): http://mini.li.ttu.ee/~nalle/tmp/DMX_PAR56contoller

Antud artiklis on juttu nö elektroonika hobiprojektist, mis siiski sai autorilt enam tähelepanu, kuna lahendust sai otsitud nii riist- kui tarkvaralisena, seda küll ilma koosdisaini metoodikat kasutamata. Sellest siis ka nihe pealkirjas – mitte riist- ja tarkvara koosdisain vaid riist- või tarkvara disain. Tulemus võib siiski väärida järeletegemist kuna valminud kontroller on küllalt universaalne seade.

Projekti algatas lihtne juhtum – tekkis vajadus lisada 3-värvilisele LED-prožektorile PAR56, mis on küll varustatud sisemise kontrolleriga ja mõningate DIP-lülitilt valitavate valmis värvusskeemide ning värvivahetusprogrammidega, täielikku häälestusulatust lubav lihtne juhtseade. Valgustusseadmete juhtimiseks on olemas ka valmispulte, kuid need olid ühe pro˛ektori kodukasutaja jaoks „liiga head“.

Nagu lähemal uurimisel selgus, on DMX (täpsemini DMX512 [1]) füüsikalisel tasandil sama, mis RS485 [2], s.t. diferentssignaali kasutav jadakoodi andmevahetusstandard. DMX protokoll on lihtne, lausa robustne – kõige lihtsamal juhul ühesuunaline andmepakett, milles iga bait tähendab infot ühe DMX kanali kohta. Konkreetne DMX-seade võib kasutada oma funktsioonide juhtimiseks mingit kanalite vahemikku paketist. Ühte paketti mahub kuni 512 kanalit, selle ulatuse ärakasutamine sõltub juba otstarbest, pakett võib olla palju lühem, olles määratud vajatavate kanalite arvuga. Pakettide vahel on paus (BREAK) loogilisel nivool „0“. Iga pakett algab minimaalselt 12µs märgisega MARK (nivool „1“), millele järgneb startkood (DMX seadmetel on üldjuhul koodiks 0x00) ja seejärel juba kanalid alates number 1-st. Jadakood saadetakse välja andmesõnadena (slot) kujul – startbitt (loogiline „0“), 8 andmebitti alates nooremast ja kaks stoppbitti (loogiline „1“). DMX standard defineerib veel pakettide vahelise pausi minimaalse kestvuse (92 µs ) ja ülekandekiiruse, milleks on üsna aukartustäratav 250kboodi – ühe bit kohta 4 µs aega. Maksimaalse paketipikkuse ja minimaalse pausi korral jõutakse sekundis saata 44 paketti, samas kui seadmed peaksid säilitama tööre˛iimi ka siis kui tuleb ainult üks pakett sekundis. Eri kanalid võivad olla mõeldud eri seadmetele kõik ühe ja sama RS485 signaaliahela (daicy-chain topoloogia) küljes. Iga seade loeb ühisest paketist välja just temale seatud kanalite andmed.

PAR56 prožektor on häälestatud reageerima paketi nelja esimese kanali andmetele, mis on siis vastavalt:

1. Punased LED-d (koodid 0-255),

2. Rohelised LED-d (koodid 0-255)

3. Sinised LED-d (koodid 0-255)

4. Heledus (koodid 0-189), vilkumine (koodid 190-250) ja mittedefineeritud (koodid 251-255).

Niisiis, lähtudes otse standardist, tuleks saata sagedusel 250kHz vähemalt kord sekundis välja 58-bitiline pakett-vektor. Juhul kui PAR56 kõigi kanalite väärtuseks on 127, oleks pakett järgmine (algus paremal):

"1101111111011011111110110111111101101111111011000000000111" ====>

Kolm „111“ alguses annavad täpselt vajaliku 12µs MARK-sündmuse.

Kui nüüd juhtseadme projekteerimiseks läheb, siis selgub, et kõige lihtsama mikrokontrolleriga seda ära ei teegi, hädavajalik on riistvaralise jadaside mooduli olemasolu (UART). Ilma selleta oleks paketi saatmine protsessorile üle jõu käiv - tavaline mikrokontrolleri töökiirus on suurusjärgus 1 µs käsutsükli kohta, mille korral jõuaks protsessor teha ühe biti väljasaatmise jooksul vaid 4 käsku – sellest ei piisa, et andmeid ette valmistada. UART moodul võtaks bitthaaval andmesõna formeerimise vaeva enda peale ja baithaaval andmeid ette sööta jõuab siis ka palju aeglasem protsessor (baidi saateaeg koos START ja kahe STOP-bitiga on 11 x 4 = 44 µs). Signaali pausiaeg on DMX korral piisavalt pikaks venitatav (kuni 1 sekund), et selle jooksul mistahes protsessor mistahes kasutajaliidese töötlemisega toime tulla.

Kuidas oleks aga riistvaraline lahend väliprogrammeeritaval kiibil? Tegelikult väga elementaarne – riistvaras võib kuitahes pikki bitivektoreid moodustada, vajalikud andmebaidid tuleb vaid vektorisse õigesse positsiooni omistada ja 250kHz taktiga väljundisse suunata. Kasutajaliidest võib riistvara töödelda paralleelselt jadakoodi väljastamisega, selleks jätkub ressursse ka kõige tagasihoidlikumas FPGA-kiibis.

-- Nexus 2 on takteeritud 50MHz signaaliga, millest teeme esmalt 25MHz signaali

kell: process(clock)

begin

if rising_edge(clock) then

clk <= not clk;

end if;

end process kell;

-- DMX jaoks 250KHz signaali tegemine 25MHz taktisignaalist

txkell: process(clk)

begin

if rising_edge(clk) then

if txclk_cnt /= 49 then

txclk_cnt <= txclk_cnt + 1;

else

txclk_cnt <=(others =>'0');

txclk <= not txclk;

end if;

end if;

end process txkell;

-- Main procedure

counting : process(txclk,reset)

begin

if reset = '1' then

DE <= '1'; -- lubav signal RS485 kiibi väljundile

txcnt <= (others =>'0'); -- tsükliloendur (pakett + paus)

dmxvector <= "1101111111011011111110110111111101101111111011000000000111";

else

if rising_edge(txclk) then

txcnt <= txcnt + 1;

if txcnt <= 1279 then –-paketitsükli kestvus 1280 x 4 us = 5.12ms

dmxvector <= '0' & dmxvector (57 downto 1); -- nihe paremale

else

txcnt <=(others =>;'0');< dmxvector <= "11" & dmxch4 & "011" & dmxblue & "011" & dmxgreen & "011" & dmxred & "011000000000111"; -- DMX pakett-vektori moodustamine

end if;

end if;

end if;

end process counting;

kell: process(clock)

begin

if rising_edge(clock) then

clk <= not clk;

end if;

end process kell;

-- DMX jaoks 250KHz signaali tegemine 25MHz taktisignaalist

txkell: process(clk)

begin

if rising_edge(clk) then

if txclk_cnt /= 49 then

txclk_cnt <= txclk_cnt + 1;

else

txclk_cnt <=(others =>'0');

txclk <= not txclk;

end if;

end if;

end process txkell;

-- Main procedure

counting : process(txclk,reset)

begin

if reset = '1' then

DE <= '1'; -- lubav signal RS485 kiibi väljundile

txcnt <= (others =>'0'); -- tsükliloendur (pakett + paus)

dmxvector <= "1101111111011011111110110111111101101111111011000000000111";

else

if rising_edge(txclk) then

txcnt <= txcnt + 1;

if txcnt <= 1279 then –-paketitsükli kestvus 1280 x 4 us = 5.12ms

dmxvector <= '0' & dmxvector (57 downto 1); -- nihe paremale

else

txcnt <=(others =>;'0');< dmxvector <= "11" & dmxch4 & "011" & dmxblue & "011" & dmxgreen & "011" & dmxred & "011000000000111"; -- DMX pakett-vektori moodustamine

end if;

end if;

end if;

end process counting;

TxDI <= dmxvector(0); -- vektori kõige parempoolne bitt väljundisse DMX-signaaliks

Tervikkirjeldusse kuulub veel komponent, mis tagab signaalide dmxred,dmxgreen, dmxblue ja dmxch4 juhtimise kasutaja poolt. Võib öelda, et kood töötas esimesest katsest, lubades pro˛ektorit vabalt juhtida ning katsetamise käigus proovida läbi erinevaid kasutajaliideseid.

Eksperiment: Tarkvaraline lahendus

Tarkvara kandjaks protsessor Microchip PIC16F88, arendustarkvaraks Microchip IDE (vabavara) ja CCS C-kompilaator PCM (kommertsprodukt [4]).

Mikrokontroller PIC16F88 on lihtne 8-bitilise arhitektuuriga 18-väljaviiguline protsessor, mis on paljude lisade hulgas varustatud asünkroonse jadaliidesega (USART). Dokumentatsiooni järgi suudab USART protsessor 4MHz sisemise takti korral genereerida vabalt 250kboodist jadasignaali.

Koodi kirjutamisel tuli tõdeda mitmeid üllatusi, mis nõudsid paljusid katseid enne kui tulemus PAR56 pro˛ektorit allutama hakkas:

1. Selgus, et PIC16F88 PortA on vaikimisi analoogsisenditena häälestatud, s.t. digitaalsisenditena kasutamiseks tuli analoogmoodul välja lülitada. Muidugi oli see ka dokumentatsioonis kirjas.

2. PIC16F88 USART ei ole otseselt häälestatav kahe stop-bitiga jadaprotokollile. Siiski, kuna andmeüksuse suurus võib olla ka 9 bitti, siis oli võimalik sättida 9-s bitt täitma esimese stopp-biti rolli (konstantselt „1“). Seda tuli siis teha väljaspool CCS PCM kompilaatori standardfunktsioone (assembleris).

3. PIC16F88 USART ei toetanud otseselt DMX protokolli. Tõsi küll, USART oskab genereerida väidetavalt RS485-toetuseks mõeldud ENABLE-signaali, mis on aktiivne andmesõna saatmise ajal, kuid ei oleks taganud vajalikku MARK signaali kestvust ja pealegi muutub ENABLE korraks passiivseks ka andmesõnade vahel, mis rikuks DMX-paketi kuju.

4. USART väljund jääb andmesõnade saatmise vaheajal kõrgeks „1“ . Kuna DMX protokoll nõuab BREAK tingimuse moodustamist, mille ajal signaal on „0“, siis lõppkokkuvõttes tuli BREAK ja MARK tingimused samuti genereerida väljaspool kompilaatori standardfunktsioone.

Nimetatud erisused tegid iseenesest triviaalse ülesande lahendamise ajakulukas ja väljundsignaali tegeliku kuju tuvastamiseks ja häälestamiseks tuli kasutada digitaalostsillograafi.

Lõppjäreldused

Riistvara (Nexys 2 ja Xilinx FPGA)

- Geomeetria: Halb, defineeritud arendusplaadi suurusega ~180cm2

- Katseplatvorm: Hea, triviaalne kodeerimine lähtudes otseselt standardist

- Arendusaeg: Tunde

- Kompileerimise/sünteesi ja mahalaadimise aeg: Minutites

- Hind: Nexys arendusplaat -$99, RS485 ajur -$3

- Geomeetria: Hea, plaadi suurus määratud protsessori ja ajurikiibi poolt ~18cm2

- Katseplatvorm: Komplitseeritud tingituna USART otsesest mittesobivusest konkreetse (DMX) protokolliga

- Arendusaeg: Päevi

- Kompileerimise/sünteesi ja mahalaadimise aeg: Sekundites

- Protsessor - $5, RS485 ajur - $3, CCS PCM C-kompilaator - $150

Tuleb tunnistada, et mõlematel variantidel on plusse ja miinuseid. Kiireks prototüüpimiseks on riistvaraline lahendus FPGA-l vägagi sobiv ja eriti ladusalt läheb standardikohase protokolli genereerimine. Samas iga arendusplaadi väline lisafunktsionaalsus nõuab väliste riistvaraliste moodulite lisamist (näiteks mikrokontrolleris on mugav sisemine EEPROM, mida võib kasutada oleku säilitamiseks seadme väljalülitatud olekus; Nexys 2 arendusplaadil tulnuks sellise funktsionaalsuse saamiseks lisada mälukaardi moodul).

Tarkvaraline lahendus sobib lõppteostuseks paremini, kuid nõuab protsessori ning kompilaatori dokumentatsiooni põhjalikku uurimist, et kõigi võimaluste ja tõkete rägastikus leida sobiv tee protokolli ja muu funktsionaalsuse teostuseks.

Lõpptulemus, nelja kanaliga ja nelja mäluga DMX kontroller koos PAR56 prožektoriga on näha järgmisel fotol:

Seadme kasutajaliidesel on neli nuppu värvide valikuks (ühtlasi ka mälupesade valikuks), nupud valitud värvi väärtuse kerimiseks ning värvuskombinatsiooni salvestus- ja taasesitusnupud.

Projektifailid on veebis [5]: PIC16F88-ga DMX-kontrolleri skeem ja trükkplaat CadSoft Eagle failidena, kontrolleri tarkvara CCS PSM C-ning kompileeritud HEX-koodis ning Nexys 2 arendusplaadile mõeldud kontrolleri tipptaseme komponendi kirjeldus VHDL keeles.

Viiteid

1. DMX512, http://en.wikipedia.org/wiki/DMX512

2. Jan Axelson, Designing RS-485 Circuits, http://lms.uni-mb.si/~meolic/students/mpk/designingRS485.pdf

3. Nexys 2 FPGA board, http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,400,789&Prod=NEXYS2

4. CCS Compilers, http://www.ccsinfo.com/content.php?page=compilers

5. Kontrolleri projektifailid (tarkvara uusim versioon dets. 2011!!!): http://mini.li.ttu.ee/~nalle/tmp/DMX_PAR56contoller

Thursday, February 11, 2010

Jõulutuled

Tuli töökaaslasega jutuks, et vaja jõuludeks mõned tuled vilkuma saada ja siin siis mu jõuluaegne projekt :-)

Alus - seitsme hõõglambikesega nn juudi kuusk. Ajast ja arust, igav-igav ja raiskab energiat, mis hirmus.

Lahendus - mikrokontrolleriga kontrollitavad kolmetoonilised LED-d, mis olid ligi aasta sahtlipõhjas sobivat hetke oodanud, tellitud SparkFun-st (vt. toote link)

Protsessor PIC12F675 - üks lihtsamaid, 8-viiguga kiip, ainult 5 programmeeritavat väljundit! Aga seda on enam kui küll kui LED-e kontrollida üle jada-rööpmuundurite 74HC595, mis on 8-bitised väljundlukkregistriga seadmed, lubades lahedalt LED-e toita (20mA väljundi kohta).

Värviheleduses 32 astet, sujuv värvide üleminek tempoga ~10 sek täisheleduseni, veenvalt maagiline, kogutsükkel mitmetes minutites ja sõltub ainult tarkvaralisest mustrist e "vaiba" pikkusest. Protsessori programmimälust kasutusel 30%, muutmälust ligi pool, töötlusjõudlusest ligi 100% (antud parameetritega, antud oludes).

Näide pildilt (päevane ja öine uduse silmaga).

Skeem ja kood, olge lahked - kingituseks, vt. siit :-) BTW - uuendatud-parandatud 2012 jaanuaris.

Lisaks (dets. 2014) - jõuluajaga seotud kolmnurgakuju ei tarvitsesugugi ainuke olla. Jõuluaeg on üürike, aga silm tahab värve näha aastaringselt. Seepärast valmis uus disain, mis sisu osas nõudis vaid nn temporaalse värvivaiba muutmist, asendamaks sümmeetriamängu eri värvide ringliikumisega. See, et disain nõudis vajaliku elengantsi saamiseks 3D-freesi ja mitmete materjalide kasutamist, on sellest blogiteemast väljaminev lugu :-)

Nexys2 õpiobjekt

5.04.2009

Niisiis, käepärast on Digilent Nexys 2 arendusplaat ja tahtmine teha üks õpiobjekt, kasutades PicoBlaze protsessorit. Mis lihtne tudengitele (need on motiveeritud ainest maksimumi omandama ja peavad teadma, mis on raamatutes kirjas), on samas raske õppejõule, sest huvi tuleb tunduvalt kaudsemalt - õppejõud peab vaid teadma, kus on raamatud.

Töövahendid

Esmalt, peab arvestama seda, et Windows XP arutu 'My Documents' kaustanimi millest Vista juures on lõpuks lahti saadud, ei sobi ISE projektifailide hoimiseks. Arendustarkvara on mingist kohast Unix põhine ja tühikut sisaldavad faili- ja kaustanimed ei käi kultuuriga kokku.

Kasutan praegu kausta C:\Projects\Nexys2

Projektiidee - stopper, resolutsiooniga 0.1 sekundit, ulatusega 0 - 9'59'9.

Kasutajaliides:

Pime otsus:

Riistvara multiplekser nõuab taktisignaali 50MHz mahajagamist 400 Hz-ni, protsessori jaoks ehk vähe, olgu seal 100kHz nagu ajaloolisel Intel 4004-l.

Esmalt õpime

Selgus, et tublid tartlased on Digilaboris ära tõlkinud-kohendanud Nexys vanema versiooni katseplaadi kasutusjuhendi ja selles leidub ka viide uuemale Nexys 2 plaadile, vaata siit.

Hoiatus - Nexys 2-l on FPGA väljaviigud hoopis teisiti ühendatud, projekti jaoks on vaja lähtuda plaadi originaaljuhendist.

Loeme läbi, mida räägivad Xilinx dokumentatsioonis PicoBlaze lühitutvustus ja kasutusjuhend UG129.

Saame esmalt teada, et Spartan 3 kiip toetab PicoBlaze järgmiste omadustega:

Lepime sellega, et Spartan 3E on lihtsalt uuemas tehnoloogias ja pisut enamate ressurssidega kui Spartan 3, s.t. kõik vanema kohta kirjapandu on rakendatav.

Käivitan ISE ja loon uue projekti File->New n2stopper, kasutades ülalnimetatud projektikausta.

Uue projekti korral tuleb sisestada vajalikud andmed kiibi kohta, s.o. Spartan 3E seeria, kiip XC3S500, korpus PG320.

Loon triviaalse VHDL tipp-tasemel mooduli n2stopper.vhdl, defineerides välisliidese kasutades taktisignaali, indikaatori ühendusi (anoodid, katoodid) ja kahte nuppu.

Arhitektuurikehas tuleb paigaldada ja siduda komponendid - PicoBlaze, selle programmimälu, strobeeritud väljundregistrid, indikaatori multiplekser, taktijagurid jne.

Projektikausta tuleb lohistada kcpsm3.vhd, mille leiab KCPSM3.zip faili (mille saab Xilinx IP keskusest PicoBlaze lehelt, vt. download - nõuab kasutaja registreerimist ja sisselogimist) VHDL alamkaustast.

Projektikausta tuleb tekitada kasutajatõkete fail (.ucf e. User Constraint Fail) n2stopper.ucf, mille abil seotakse FPGA väljaviigud konkreetsete VHDL signaalidega.

Tuleb kirjutada assembler, esialgu ainult testfunktsionaalsuses ja see assembleerida. Selleks on vaja KCPSM3.zip faili Assembler alamkaustast kopeerida projektikausta 4 faili - KCPSM3.EXE, ROM_form.vhd, ROM_form.v ja ROM_form.coe. Assemblerfaili nimeks panen prog_rom.psm, sest assembleerimisel loodava VHDL üksuse nimi võetakse failinimest ja üksus nimega prog_rom esineb koodinäidetes. Õnnestunud assembleerimine genereerib seega faili prog_rom.vhd.

Järgnevalt tuleb ISE-s projektifailide hulka lisada (juba olemasolevale n2stopper.vhdl failile) n2stopper.ucf, kcpsm3.vhd ja prog_rom.vhd.

Järgneb süntees... ISE Process->Implement top module

Järgnevad veateated, pole sa mingi "VHDL-i isa" :-)

Järgneb koodi s.t. n2stopper.bit faili genereerimine - läheb probleemideta.

Bit faili laadimiseks Nexsys plaadile tuleb kasutada sellega komplektis olevat USB-liidesega laadurit.

Voila! Toimib! Indikaatoril aeg jookseb, tarkvaraline loendamine displeil just soovitud kujul pärast RESET-i. M.o.t.t.

Ja samas, niipea kui koodi parendama hakkasin, nägin ainult riistvara toimimas, loendumine ehk siis protsessor seisab. Kummaline, et loenduri käitumine sõltus sellest, et kas viite arvutamisel kasutatakse ülesloendava registri algväärtusena kuueteistkümnendarvu ef või f0 - esimesel juhul OK, teisel juhul asi RESET-st edasi ei liigu. Absurdne.

Aga selge, järgnevalt tuleb läbi proovida Xilinx enda soovitatud intelligentsem assembler ja simuleerida lahendusi enne genereerimisi, hoiab kõvasti aega kokku.

****

6.04.2009

Midagi oli mäda taktisignaalidega. Päris põhjust ei õnnestunudki kätte saada, probleem ujus eest ära.

Oletasin, et CLK puhvrid pole adekvaatselt paigas ja seepärast PicoBlaze ei tööta. Asendasin jagatud takti originaaltaktiga, mis peaks igal juhul olema korralikult puhverdatud ja tõepoolest, tarkvaras esitatud funktsionaalsus taastus. Arendasin tarkvara, kõik eri sünteesid andsid oodatud tulemusi ja lõpuks proovisin uuesti madalama sagedusega jagatud taktiga PicoBlazele.

Töötas! Aru ma ei saa :-) Normaalne inseneri elu.

Aga edasiseks mõtteks - uurida tõkete juhendit (Xilinx constraint guide), et oskaks .ucf failiga midagi arukat sünteesi juhtimiseks öelda.

20.04.2009

Täitsa abiks asi on Mediatronix-i pBlaze IDE, mis sisaldab normaalset süntaksit järgivat ning värvivat redaktorit ja simulaatorit. Assembleri süntaks ja mnemoonika pisut erineb Xilinxi PicoBlaze originaalsüntaksist, aga see pole probleem. Isegi Xilinx kiidab pBlaze IDE-t oma kasutusjuhendis UG129.

KCPSM3 originaalassembleri oskab pBlaze IDE muretult oma süntaksisse ja vormingusse importida.

Selleks, et pBlaze IDE lõpuks püsimälu sisule vastava VHDL faili genereeriks, tuleb assemblerfaili viimaseks käsuks panna direktiiv VHDL (vt. direktiivid):

Sellisel juhul genereeritakse assembleerimisel samad väljundfailid nagu KCPSM3 korralgi. Esimene parameeter on ROM-i alusfail, teine parameeter on väljundfaili ja kolmas genereeritava ROM-üksuse (entity) nimi.

Voila!

Ja lõpuks - loodud failidega saab tutvuda siin. See on ainult mäng ju.

Niisiis, käepärast on Digilent Nexys 2 arendusplaat ja tahtmine teha üks õpiobjekt, kasutades PicoBlaze protsessorit. Mis lihtne tudengitele (need on motiveeritud ainest maksimumi omandama ja peavad teadma, mis on raamatutes kirjas), on samas raske õppejõule, sest huvi tuleb tunduvalt kaudsemalt - õppejõud peab vaid teadma, kus on raamatud.

Töövahendid

- Arendusplaat Xilinx XC3S500E kiibiga, FG320 korpus, toide USB liidese kaudu

- Digilent Adept Suite plaadile koodi mahalaadimiseks

- Xilinx ISE 10.1.03 integreeritud arenduskeskkond (60 päeva prooviversioon)

Esmalt, peab arvestama seda, et Windows XP arutu 'My Documents' kaustanimi millest Vista juures on lõpuks lahti saadud, ei sobi ISE projektifailide hoimiseks. Arendustarkvara on mingist kohast Unix põhine ja tühikut sisaldavad faili- ja kaustanimed ei käi kultuuriga kokku.

Kasutan praegu kausta C:\Projects\Nexys2

Projektiidee - stopper, resolutsiooniga 0.1 sekundit, ulatusega 0 - 9'59'9.

Kasutajaliides:

- Sisend: kaks nuppu: START/STOP ja RESET

- Väljund: 4-järguline 7-segmendiline indikaator, laotussagedusega 400 Hz (s.t. üksiku järgu vilkumissagedus 100Hz)

Pime otsus:

- Riistvaras teeme laotuse (väljundi multiplekseri ja 7-segmendi dekoodri indikaatorile) ja indikaatoril eralduspunktide genereerimise sekundikümnendike, sekundite ja minutite eraldamiseks.

- Tarkvaras, s.o. PicoBlaze assembleris saab olema stopperi põhifunktsionaalsus - nuppude jälgimine, loendamine ja loendusmooduli kontroll (nt. 60 sekundit on üks minut, eks).

- Riist- ja tarkvara liides kõige lihtsamal kujul sisaldab nelja registrit, millest igaüks sisaldab kahendkoodis vastava indikaatori järgu väärtust.

Riistvara multiplekser nõuab taktisignaali 50MHz mahajagamist 400 Hz-ni, protsessori jaoks ehk vähe, olgu seal 100kHz nagu ajaloolisel Intel 4004-l.

Esmalt õpime

Selgus, et tublid tartlased on Digilaboris ära tõlkinud-kohendanud Nexys vanema versiooni katseplaadi kasutusjuhendi ja selles leidub ka viide uuemale Nexys 2 plaadile, vaata siit.

Hoiatus - Nexys 2-l on FPGA väljaviigud hoopis teisiti ühendatud, projekti jaoks on vaja lähtuda plaadi originaaljuhendist.

Loeme läbi, mida räägivad Xilinx dokumentatsioonis PicoBlaze lühitutvustus ja kasutusjuhend UG129.

Saame esmalt teada, et Spartan 3 kiip toetab PicoBlaze järgmiste omadustega:

- Programmi mälu - 1024 18-bitist sõna

- 16 8-bitist registrit

- Pinu 31 sõna

- Assembler KCPSM3

- Maht 96 Spartan-3 lõiku (slice) - pisiasi, sest XC3S500E-s on kokku 4656 lõiku

- Tootlus 44 MIPS-i

Lepime sellega, et Spartan 3E on lihtsalt uuemas tehnoloogias ja pisut enamate ressurssidega kui Spartan 3, s.t. kõik vanema kohta kirjapandu on rakendatav.

Käivitan ISE ja loon uue projekti File->New n2stopper, kasutades ülalnimetatud projektikausta.

Uue projekti korral tuleb sisestada vajalikud andmed kiibi kohta, s.o. Spartan 3E seeria, kiip XC3S500, korpus PG320.

Loon triviaalse VHDL tipp-tasemel mooduli n2stopper.vhdl, defineerides välisliidese kasutades taktisignaali, indikaatori ühendusi (anoodid, katoodid) ja kahte nuppu.

Arhitektuurikehas tuleb paigaldada ja siduda komponendid - PicoBlaze, selle programmimälu, strobeeritud väljundregistrid, indikaatori multiplekser, taktijagurid jne.

Projektikausta tuleb lohistada kcpsm3.vhd, mille leiab KCPSM3.zip faili (mille saab Xilinx IP keskusest PicoBlaze lehelt, vt. download - nõuab kasutaja registreerimist ja sisselogimist) VHDL alamkaustast.

Projektikausta tuleb tekitada kasutajatõkete fail (.ucf e. User Constraint Fail) n2stopper.ucf, mille abil seotakse FPGA väljaviigud konkreetsete VHDL signaalidega.

Tuleb kirjutada assembler, esialgu ainult testfunktsionaalsuses ja see assembleerida. Selleks on vaja KCPSM3.zip faili Assembler alamkaustast kopeerida projektikausta 4 faili - KCPSM3.EXE, ROM_form.vhd, ROM_form.v ja ROM_form.coe. Assemblerfaili nimeks panen prog_rom.psm, sest assembleerimisel loodava VHDL üksuse nimi võetakse failinimest ja üksus nimega prog_rom esineb koodinäidetes. Õnnestunud assembleerimine genereerib seega faili prog_rom.vhd.

Järgnevalt tuleb ISE-s projektifailide hulka lisada (juba olemasolevale n2stopper.vhdl failile) n2stopper.ucf, kcpsm3.vhd ja prog_rom.vhd.

Järgneb süntees... ISE Process->Implement top module

Järgnevad veateated, pole sa mingi "VHDL-i isa" :-)

Järgneb koodi s.t. n2stopper.bit faili genereerimine - läheb probleemideta.

Bit faili laadimiseks Nexsys plaadile tuleb kasutada sellega komplektis olevat USB-liidesega laadurit.

Voila! Toimib! Indikaatoril aeg jookseb, tarkvaraline loendamine displeil just soovitud kujul pärast RESET-i. M.o.t.t.

Ja samas, niipea kui koodi parendama hakkasin, nägin ainult riistvara toimimas, loendumine ehk siis protsessor seisab. Kummaline, et loenduri käitumine sõltus sellest, et kas viite arvutamisel kasutatakse ülesloendava registri algväärtusena kuueteistkümnendarvu ef või f0 - esimesel juhul OK, teisel juhul asi RESET-st edasi ei liigu. Absurdne.

Aga selge, järgnevalt tuleb läbi proovida Xilinx enda soovitatud intelligentsem assembler ja simuleerida lahendusi enne genereerimisi, hoiab kõvasti aega kokku.

****

6.04.2009

Midagi oli mäda taktisignaalidega. Päris põhjust ei õnnestunudki kätte saada, probleem ujus eest ära.

Oletasin, et CLK puhvrid pole adekvaatselt paigas ja seepärast PicoBlaze ei tööta. Asendasin jagatud takti originaaltaktiga, mis peaks igal juhul olema korralikult puhverdatud ja tõepoolest, tarkvaras esitatud funktsionaalsus taastus. Arendasin tarkvara, kõik eri sünteesid andsid oodatud tulemusi ja lõpuks proovisin uuesti madalama sagedusega jagatud taktiga PicoBlazele.

Töötas! Aru ma ei saa :-) Normaalne inseneri elu.

Aga edasiseks mõtteks - uurida tõkete juhendit (Xilinx constraint guide), et oskaks .ucf failiga midagi arukat sünteesi juhtimiseks öelda.

20.04.2009

Täitsa abiks asi on Mediatronix-i pBlaze IDE, mis sisaldab normaalset süntaksit järgivat ning värvivat redaktorit ja simulaatorit. Assembleri süntaks ja mnemoonika pisut erineb Xilinxi PicoBlaze originaalsüntaksist, aga see pole probleem. Isegi Xilinx kiidab pBlaze IDE-t oma kasutusjuhendis UG129.

KCPSM3 originaalassembleri oskab pBlaze IDE muretult oma süntaksisse ja vormingusse importida.

Selleks, et pBlaze IDE lõpuks püsimälu sisule vastava VHDL faili genereeriks, tuleb assemblerfaili viimaseks käsuks panna direktiiv VHDL (vt. direktiivid):

VHDL "ROM_form.vhd", "prog_rom.vhd", "prog_rom"

Sellisel juhul genereeritakse assembleerimisel samad väljundfailid nagu KCPSM3 korralgi. Esimene parameeter on ROM-i alusfail, teine parameeter on väljundfaili ja kolmas genereeritava ROM-üksuse (entity) nimi.

Voila!

Ja lõpuks - loodud failidega saab tutvuda siin. See on ainult mäng ju.

Subscribe to:

Posts (Atom)